Single cycle implementation:

- 한 사이클에 한 명령어를 완전히 실행한다.

- 모든 명령어가 동일한 시간을 소요한다.

- 구현이 간단하지만 성능이 제한적이다.

- 각 하드웨어 단계를 한 명령어에만 사용한다.

Pipeline implementation:

- 명령어 실행을 여러 단계로 나누어 처리한다.

- 여러 명령어를 동시에 다른 단계에서 처리한다.

- 전체적인 처리량이 증가한다.

- 하드웨어를 더 효율적으로 사용한다.

- 구현이 복잡하며 파이프라인 해저드 관리가 필요하다.

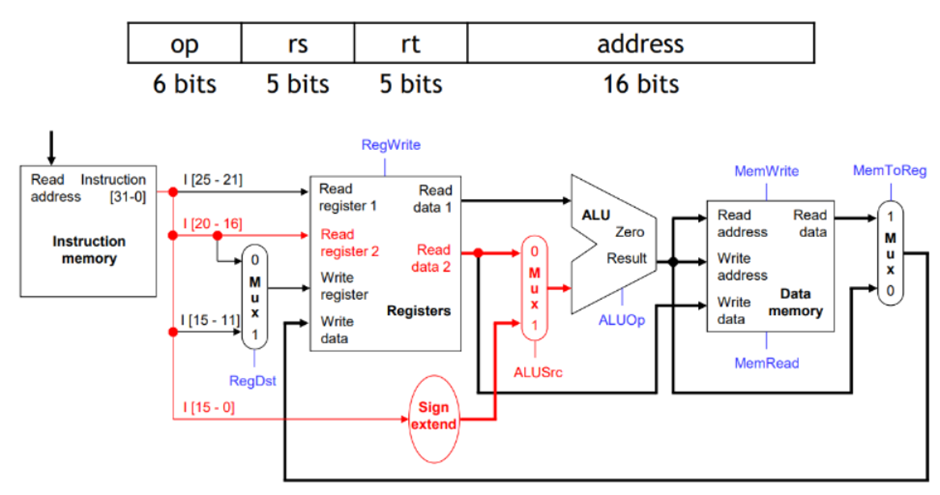

Instruction fetch

Instruction fetch 단계는 다음과 같이 작동한다:

- Instruction memory에 32비트 명령어가 주소에 맞게 저장되어 있다.

- PC(Program Counter)가 instruction memory에 명령어 주소를 제공한다.

- 해당 주소의 명령어를 가져와 실행한다.

- PC 값을 4만큼 증가시켜 다음 명령어를 준비한다.

Instruction decording

Instruction decoding 단계는 다음과 같이 작동한다:

- 각 레지스터를 5비트로 표현한다.

- 한 번에 최대 2개의 레지스터만 읽을 수 있다.

- Regwrite 신호로 레지스터 업데이트를 제어한다:

- 1이면 레지스터를 읽고 쓴다.

- 0이면 레지스터에 쓰지 않는다

Executing R-type instruction

R-type 명령어 실행 과정은 다음과 같다:

- 두 개의 레지스터 값을 읽어온다.

- ALU를 사용하여 이 값들을 계산한다.

- 계산 결과를 목적지 레지스터에 저장한다.

Decoding I-type instructions

I-type 명령어 처리 과정은 다음과 같다:

- I-type 구조는 op, rs, rt, address로 구성된다.

- RegDst mux로 I-type 또는 R-type 형식 선택을 결정한다.

- address를 32bit로 확장하기 위해 sign extend를 수행한다.

- ALU 출력 사용 시 MemToReg는 0, Data memory 출력 사용 시 1로 설정한다.

- Beq 명령어 실행 시:

- offset에 4를 곱하기 위해 shift left 2를 수행한다.

- 결과를 pc+4에 더한다.

- PCSrc를 1로 설정하고, 그 외의 경우 0으로 설정하여 pc+4를 유지한다.

Executing an J-type instruction

J-type 명령어 실행 과정은 다음과 같다:

- 주소 값을 shift left 2로 4배 증가시킨다.

- 증가된 값에 4를 더한 후 PC에 넣는다.

여러 종류의 명령어를 하나의 회로에서 처리하기 위해서는:

- Control path에서 나오는 control signal을 적절히 조정한다.

- 이를 통해 각 명령어 유형에 맞는 동작을 수행할 수 있도록 한다.

'학교공부 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터 구조] VLIW and Superscalar (3) | 2024.10.13 |

|---|---|

| [컴퓨터 구조] Branch prediction (0) | 2024.10.13 |

| [컴퓨터구조] Cache (0) | 2023.06.09 |

| [컴퓨터 구조] Memory Hierarchy (0) | 2023.06.03 |

| [컴퓨터 구조] Multithreading (0) | 2023.06.03 |